Toshiba develops the new chip memory BiCS to 48 layers

For some time the NAND flash chips, especially those intended for SSD, are able to take advantage of a 3D structure at the level of individual cells in the package. A concrete example comes from Samsung, with chips 24 and 32 layers used in the latest SSD lines. The advantages are numerous, not least to be able to achieve higher capacities in relation to the space occupied and increasingly higher performance.

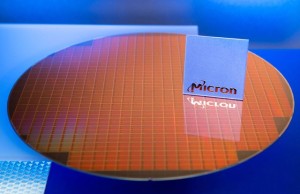

Recently, Intel and Micron have chosen a similar path in the development and definition of the roadmap referred to the NAND flash chips, which we discussed in this news. No wonder then that even a giant like Toshiba presents their generation of NAND flash chips in multiple layers while setting a record as to the number or as many as 48.

The statement Toshiba is really concise, which is why we are not in a position to go down very detailed; what is known is that the technology is called BiCS and that the type of chip is a 2-bit per cell, with a package of 128 Gigabit (or 16GB, which combined with other identical then go on to form the total quantity in terms of capacity an SSD).

Source: Toshiba