Qualcomm expects to see 3D-SoC layout next year

At the conference, International Symposium on Physical Design 2015 (ISPD 2015) heads the engineering group company Qualcomm, Karim Arabi, said the company expects to see the first Qualcomm SoC experienced using volumetric layout in the next year. Layering crystals allow halve the landing area and processors at the same time increase product yield. But the interesting thing is that, Qualcomm will refuse connections crystals in the stack using the increasingly popular through TSVs-connections.

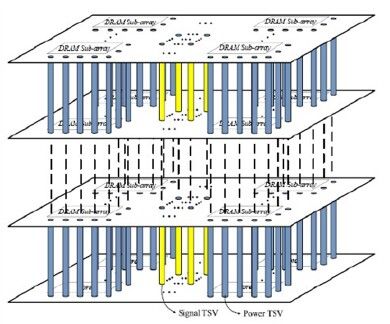

Through connection by TSVs – it’s the same metallization channels, but only with the use of extremely thin holes. Such channels in the crystal can be tens or hundreds of thousands. And each channel captures large usable area on the chip, significantly greater than the diameter of the layer – it is an area set aside to compensate for the strain at working heating circuits. With TSVs-memory connections, today issued SK Hynix HBM and Micron HMC, as well as flash memory 3D NAND with 32 or 48 layers. But what is good for regular structures, confident in Qualcomm, something bad for VLSI.

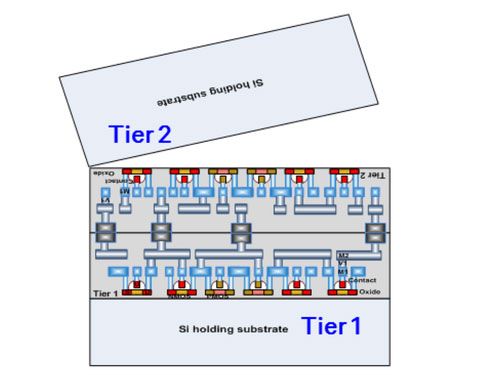

Among considering two options to package chips SoC stack. Note, Qualcomm has not yet expect to see demand for assembly of more than two crystals. In rare cases, it could be a stack assembly of three crystals, where the second and third crystals can be considered as an auxiliary, for example, separate cellular modem and something else. Mainly produced are double-crystal structure. For this method can be used as a coherent assembly and the counter.

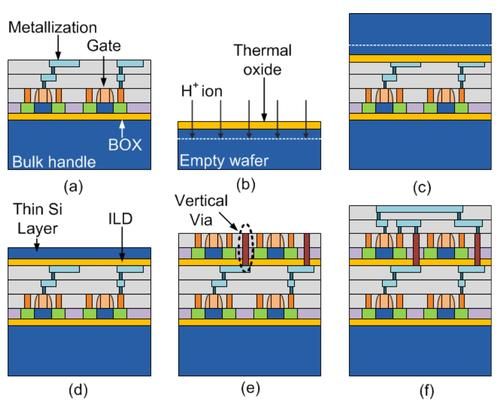

The method of assembly involves the creation of the second crystal directly on top (working) of the first crystal. After fabrication of the lower crystal on top of it overlaps (deposited) silicon layer, which creates a second crystal. Such a method makes it possible to manufacture the serial connect the upper and lower crystals relatively small diameter channels metallization, although they are a hundred times more TSVs-channels. The problem here is that the annealing of the plate during the manufacturing process requires the crystal temperature of 1200 degrees Celsius. This melt all the copper compound in the lower die. Copper can replace the tungsten refractory, but this would reduce the clock frequency. You can also reduce the annealing temperature, but it also reduces the clock frequency due to the deterioration of the semiconductor in the transistor channel.

Avoid these drawbacks by using the counter arrangement of crystals. Both crystals are produced each in its process technology and only then connect them to the ends where there are special pads. This method can provide comparatively high precision alignment pads, so the size of the contact areas must be large, which is not good. Therefore, according to Qualcomm, future 3D-SoC chips are likely to combine both methods in optimal proportions.

It is worth saying that the company is IBM, which is also engaged in similar issues with the European center Leti, expects to start production of an experienced 3D-SoC in 2017 or in 2018. In other words, the script Qualcomm them seems too optimistic. On the other hand, Samsung has launched a 3D NAND ahead of competitors in almost two years. Therefore, you should never say never. However, Qualcomm is based on the technical processes TSMC, and the latter has no technical processes capable of in the near future to ensure the release of 3D-SoC layout and use of TSVs. Perhaps it is linked to “torment” Qualcomm over the search options in the production of processors stack layout.